There is currently significant excitement and interest in the market surrounding cloud computing. Office applications and social media platforms including Outlook, Gmail, Instagram, and Twitter, leverage remote servers for uninterrupted service. Typically, our devices, such as mobile phones and computers, became as transceivers to communicate with distant servers over a network, exchanging data to enable various functions and services

I saw many using even calculator online. This might give a perception that edge devices don’t need much computational power. Emerging requirements have necessitated the implementation of localized AI algorithms, particularly for security-centric applications like facial recognition, to ensure enhanced privacy and functionality. The result was a new wave of RISC-based processors, engineered to pack a punch in terms of computational power.

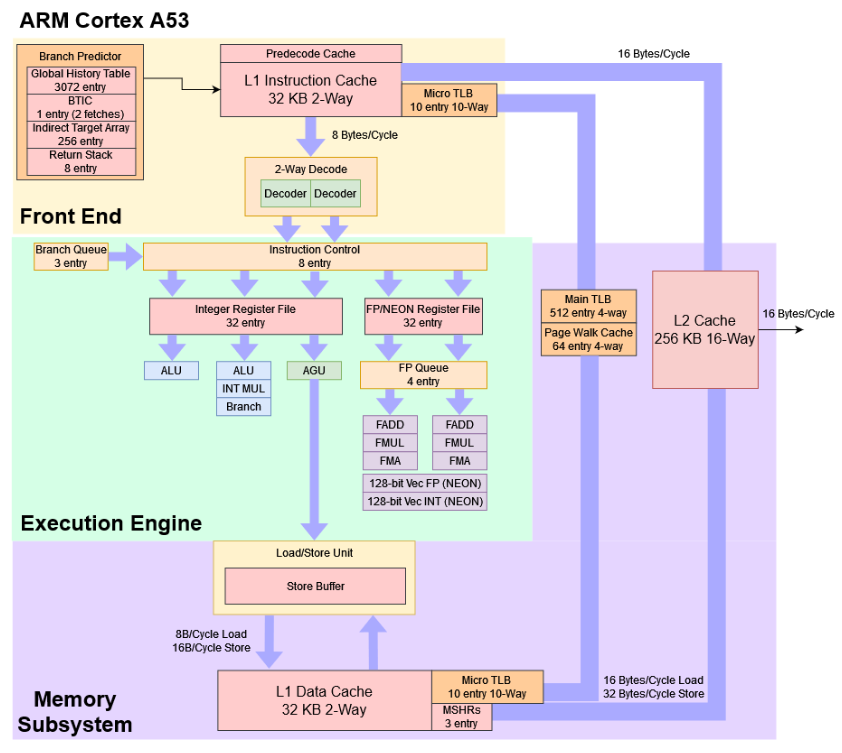

I did some research online and tried to understand some of the branded processors that are in the market like Snapdragon series, MediaTek series etc., and surprised to see these processors are using ARM cortex A50 series cores within them. Arm Cortex A50 series is introduced in 2012 by ARM based on ARMv8 architecture. Among the Cortex A50 series, the Cortex A53 stands out for its optimized design, prioritizing efficiency and power management. It is the reason this CPU is widely used in smartphones, tablets, and other devices.

List of Popular CPU sets uses ARM Cortex-A53

For a quick overview of Cortex A53 Armv8-A Instruction Set Architecture

Figure credits: ARM’s Cortex A53: Tiny But Important – Chips and Cheese

The above picture gives a glimpse of ARM Cortex-A53.

Yes, It’s a very complicated diagram. But don’t worry, I am here to help you out. I will pick some of the crazy concepts and unbox them for you in easiest way possible.

One of the interesting topics is Out of order execution. Many Arm processors use out of order execution. Wait, I just threw a new term. Right? Let me explain.

Any standard processor uses in-order pipelining. This is a well-known standard where we have Fetch, Decode and Execute pipeline stages. Every instruction is Fetched, Decoded and executed by the processor as per the order they are in the program code. To reduce latency parallelism is introduced such that if one Instruction completes Fetch stage, it is pushed to decode stage, and another instruction comes into fetch stage. Likewise, in decode and execute stages. Everything is smooth till here. Now let me put in some problem. Due to some issues like loading operand from main memory caused by a cache miss, your instruction fetch took more CPU cycles. This will affect the whole upcoming instructions to get stalled.

To overcome such cases ARM processors, use Out of order execution. In this process, if consecutive instructions don’t depend on each other than their execution can go out of order. Taking up the same example above: if the successive instruction doesn’t depend on the load instruction it can go ahead in pipeline stages while the operand loading is in progress.

To dive into detailed design implementation, click here Lecture 5: Out-of-order Execution (tamu.edu).

This might give you an understanding of what is out of order execution. It improves the performance of processors.

ARM cortex – A53 uses in-order execution. Aww!…

Yes, ARM Cortex-A53 uses in-order execution still it beats the speed of mighty out of order execution. But Why??

In the beginning we started with saying Cortex-a53 is the most power efficient system right. Out or order execution requires hardware that consumes more power. So A53 sticks with in-order execution. Then how can it overtake the speed of out of order execution. ??

Here comes the first left topmost block in the above ARM cortex A53 diagram.

Branch predictor …

Curious to know how it works …

Then wait till the next blog ….